Inhalt: Erfahrungen und Kenntnisse

FPGA Entwicklung mit VHDL auf ALTERA (jetzt INTEL) und XILINX

Wir haben unten stehend für Sie ein paar relevante Kunden-Projekte aufgelistet, um Ihnen einen Überblick über unsere Erfahrungen und Kenntnisse zu geben:

High-Speed Signalanalyse mit FPGA und High Performance ADU

Eine Anwendnung in einem Forschungsprojekt verlangte die Erfassung von Eingangssignalen mit sehr hoher Auflösung (4ns). Das Eingangssignal wurde mit 0,5V bis 2,0V, repitierend und mit einer Flankensteilheit von etwa 500ns definiert.

Das eingesetzte FPGA, ein XILINX KINTEX 7 (xc7k160tfbg676-1), sollte das komplette Signal in Echtzeit erfassen und auf Gültigkeit hin prüfen. Eine Störimpulserkennung mit entsprechender Datenkorrektur rundeten die Aufgabe ab.

Um diese Aufgabe erfüllen zu können, musste ein sehr schneller AD-Umsetzer AD9494 der Firma ANALOG-DEVICE eingesetzt werden. Mit 250MS/s setzte der ADU das Analogsignal in die digitale Welt um und stellte die Daten über ein paralles 12Bit-breites Bussystem mit LVDS-Ankopplung dem FPGA zur Verfügung.

Im FPGA gab es zwei Clockdomainen: eine mit 100MHz für die SPI-Anbindung/Steuerung zu einem externen Mikroprozessor und eine mit 250MHz für die interne Echtzeit-Signalverarbeitung. Die sich daraus ergebene Systemauflösung betrug 4 nsek.

Umsetzung:

VHDL-Entwicklung auf XILINX KINTEX 7 mit XILINX VIVADO

Permalink: high-speed-signalanalyse

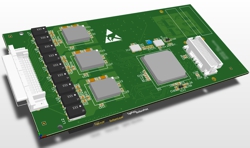

XMC-Baugruppe mit PCIe, einem FPGA als Bridge und Kommunikations-Hardware

Für einen Industrie-PC (6U CompactPCI Processor Board) sollte eine XMC-Karte (PCIe 2.0) entwickelt werden, die die Baugruppe mit einer PCIexpress-Lane (1x) an ein FPGA XILINX ARTIX 7 (xc7a75tfgg484-2) anbindet.

Das FPGA sollte als Bridge zwischen dem PC und der Kommunikations-Hardware fungieren.

Umsetzung:

Baugruppenentwicklung und VHDL-Design auf XILINX ARTIX 7 mit XILINX VIVADO

Permalink: XMC-Baugruppe mit PCIe 2.0

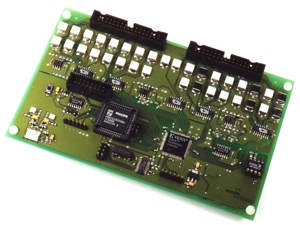

PCIe-PC-Karte mit einer Lane und zwei FPGAs

Die Aufgabe war, eine PCIe-Steckkarte (PCIexpress 1.1) für PCs zu entwickeln. Auf der Seite des Edge-Connectors (PCI-Express-Slot) nahm ein ALTERA FPGA CYCLONE 4GX (EP4CGX15BF14I7N) die PCIexpress Lane entgegen.

Das FPGA fungierte hier als Bridge zu einem Innovasic FIDO 5000 REM, der als Communication Controller eine Schnittstelle zu PROFINET, EtherNet/IP, ModbusTCP, EtherCAT, SERCOS und POWERLINK bietet.

Umsetzung:

Baugruppenentwicklung und VHDL-Test-Design mit ALTERA QUARTUS II und ModelSIM.

Permalink: PCIe-PC-Karte mit FIDO 5000 REM

PID-Reglungen von Laserleistung und Kühlung in einem Medizin-Produkt per FPGA

Im konkreten Fall mussten wir eine gescheiterte Entwicklung eines grossen niederländischen Konzerns auf Basis eines ALTERA CYCLONE 3 (EP3C25Q240C8N) übernehmen, uns in deren Quellcodes (110 Dateien) einarbeiten, Fehler finden und diese beseitigen sowie neue Funktionen integrieren.

Da der ursprünglich entwickelte PID-Regler für die Laserleistung gar nicht funktionierte, mussten wir hier von Null auf neu beginnen und konnten die Entwicklungsziele unseres Kunden zur besten Zufriedenheit erreichen.

Der PID-Regler war als VHDL-Code im FPGA untergebracht.

Umsetzung:

VHDL-Design mit ALTERA QUARTUS II und ModelSIM.

Permalink: FPGA-PID-Reglungen von Laserleistung

Auswertesystem für Echtzeit-Sensordaten in einem FPGA

Entwicklung einer Echtzeitauswertung von digitalisierten Signalen mehrerer CMOS-Zeilenkameras auf einem XILINX SPARTAN 3ADSP (XC3SD1800A-BGA484) in VHDL.

Die Echtzeitdaten werden mit einfachen mathematischen Zusammenhängen bearbeitet und anschließend gegen einen Schwellwert überprüft.

Anbindung des FPGA an einen Mikrocontroller TEXAS TMS320.

Umsetzung:

VHDL-Design mit XILINX ISE, XILINX ISIM und Mentor ModelSIM.

Permalink: Echtzeit-Sensordaten mit FPGA

Messsystem zur Auswertung von Werkzeugverschleiß an Hartmetalschneiden (CBN)

FPGA-System basierend auf einem ALTERA CYCLONE 3 mit integriertem NIOS II-Mikrocomputer, Ethernet- und DDR-RAM-IP-Cores, eine Signalauswertungshardware in VHDL sowie einem vorgeschaltetem schnellen AD-Umsetzer (TEXAS ADS1605 5MS/s) zur Datenverarbeitung und zum Handling der Signale.

Innerhalb des FPGAs wurde die Module mit dem AVALON-Bus an die NIOS II-CPU angebunden.

Die Signalbearbeitung umfasste die Aquisition von analogen Werten in Blöcken a 1024 Werten, eine Fensterung, eine FFT-Analyse sowie eine Aswertung des Spektrums.

Die Entwicklung erfolgte in einem Team zu dritt, wobei unser Anteil die Signalauswertung und das Datenhandling auf dem FPGA in VHDL war.

Umsetzung:

VHDL-Design mit ALTERA QUARTUS II und Mentor ModelSIM.

Permalink: Auswertung von Werkzeugverschleiß

System zur Auswertung von Mikroerodierimpulsen

Auswertung von LWL-Signale mit einem XILINX SPARTAN XL (XCS05XL-5VQ100C) und Weiterleitung an zur PC-Steuerung und zu einem D-Space-System.

Umsetzung:

VHDL-Design mit XILINX ISE und Mentor ModelSim.

Permalink: Auswertung von Mikroerodierimpulsen

Entwicklung einer induktiven Sensormatrix zur Erfassung von Dartpfeilen

Entwicklung einer Auswerteelektronik für eine normale Sisal-Dartscheibe mit austauschbarem Gitter.

In die Scheibe eindringende Pfeile wurden induktiv erfasst.

Ein an einem XILINX FPGA SPARTAN XL (XCS05XL-5VQ100C) angeschlossener Mikrocontroller (8051-Derivat) der Firma Philips lokalisierte letztendlich das getroffene Feld und steuerte eine Anzeige an.

Diese Entwicklung wurde im Team zu zweit mit einem Diplomanten durchgeführt, wobei unser Anteil die Konzeption und Entwicklung des Gesamtsystems sowie die Entwicklung der Elektronik und des FPGAs war.

Diese Entwicklung führte zu einem deutschen Patent und zu einigen Veröffentlichungen in der Zeitschrift Elektronik.

Umsetzung:

Kernkomponente 8051-Mikrocontroller und ein XILINX SPARTAN XL FPGA, welches in VHDL mit der Software XILINX ISE und Mentor ModelSIM entwickelt wurde.

Permalink: Erfassung von Dartpfeilen

weitere Erfahrungen und Kenntnisse:

Qualitätsmanagement nach

DIN EN ISO 9001:2015

Mitglied im

Fachverband für Elektronik-Design

und -fertigung e.V. (FED)