Inhalt: Überprüfung Ihres Elektronikdesigns, Schaltplan und Layout

Es gibt in der Praxis durchaus Fälle, wo Unternehmen gerne von einem externen Experten ein neues oder bestehendes Elektronikdesign / Schaltung einer elektronischen Flachbaugruppe auf Designfehler hin überprüfen lassen wollen.

Sei es aus Gründen der Qualitätssicherung oder auch um Entwicklungsschleifen zu minimieren.

Das soll in erster Linie keine Verurteilung, Diskreditierung oder Demütigung der eigenen Entwicklungsingenieure darstellen, sondern ganz neutral Schaltungsfehler und Layoutfehler schon im Vorfeld durch ein Vier-Augen-Prinzip erkennen.

keine Diskreditierung der eigenen Entwicklungsingenieure

Auch Ihre hoch spezialisierten Entwicklungsingenieure machen manchmal Fehler oder übersehen eine Kleinigkeit in den Datenblättern von IC-Herstellern, was eine großer Wirkung auf die Funktion haben kann.

Unter diesen Randbedingungen bewerte ich nicht die Entwickler des Elektronikdesigns, sondern ausschliesslich den Schaltplan oder das Layout als solches.

So kommt es bei einer solchen Überprüfung auch zu einem Wissenstransfer in Richtung Auftraggeber, denn ein früh erkannter Fehler, kann im Idealfall auch bei neuen / weiteren Elektronikdesigns berücksichtigt werden.

Ein weiterer sinnvoller Einsatz einer Design-Überprüfung ist, vor einer Schaltungs-Revision die bestehende Schaltung auf Fehler und Optimierungspotenzial zu untersuchen und das Ergebnis zum neuen Anforderungskatalog (Lastenheft / Pflichtenheft) hinzuzufügen.

auf welcher Weise erhalte ich die Überprüfungsergebnisse?

Im Normalfall erstelle ich Ihnen eine sehr ausführlich begründete Zusammenfassung der kritischen Stellen, die mit Screenshots oder Datenblattauszügen unterstrichen werden.

Die letzten erstellten Design-Überprüfungen hatten einen Umfang von 20-25 PDF-Seiten.

wie erfolgt die Abrechnung dieser Dienstleistung?

Die Abrechnung einer Analyse bzw. Beratung erfolgt nach Zeitaufwand. Sie erhalten mit der Abschlussrechnung einen Auszug der Zeiterfassung, mit detaillierter Auflistung der Tätigkeiten im Projekt.

Kontakt für Anfragen zu Design-Überprüfungen

Für Anfragen zu Gutachten nutzen Sie bitte mein Kontaktformular.

Benötigen Sie eine Gutachten für Ihre Elektronik?

Auf der Seite Sachverständiger / Gutachter können Sie sich auch gerne über meine Dienstleistungen im Bereich der Gutachten informieren.

Fall-Beispiele für entdeckte Fehler bei Design-Überprüfungen:

Designfehler: Massefläche - "Fill and Pray"

Für eine stabile Versorgung von Elektronikkomponenten auf Leiterplatten, ist eine gute Masse-Anbindung (Ground / GND) unbedingt notwendig. Sie sorgt dafür, dass Rückflüsse von Signalströmen und Versorgungsströmen Nieder-Ohmig und Nieder-Induktiv von der Quelle zur Senke fliesen können.

Ein wichtiger Parameter in diesem Thema ist die Anzahl der verfügbaren Lagen (Verdrahtungsebenen) der zu designenden Leiterplatte.

In einem Multilayer mit 4 Lagen oder mehr, werden sehr häufig mehrere Lagen für Versorgungsspannungen und Masse verwendet. Vollflächig ausgelegt sind die beiden Hauptaugenmerke "Nieder-Ohmig" und "Nieder-Induktiv" prinzip bedingt gut umgesetzt.

Was ist aber, wenn nur zwei Lagen zur Verfügung stehen oder bei einem 4 Lagen Multilayer alle Ebenen für die Verdrahtung benötigt werden?

Erfahrene Elektronikentwickler und Layouter erarbeiten sich vor Beginn der Entflechtung ein Konzept aus, wie Versorgungsspannungen und Masseführung im Einklang mit den Signalleitungen stehen können.

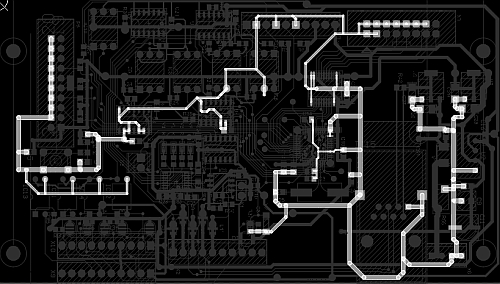

Ungeübte Layouter hingegen verlegen zuerst die Signalleiterbahnen und fluten dann die Ebenen mit einem Polygon-Fill mit Masse oder Versorgungsspannung. Nach dem Motto "Fluten und Beten", dass es funktioniert!

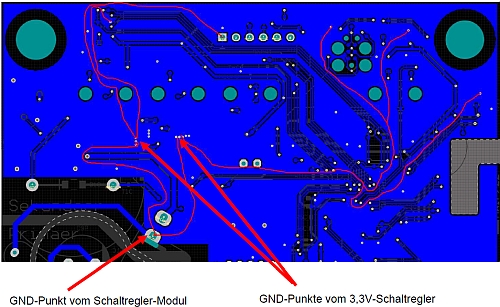

Genau so einen Fall hatte ich in einer Design-Überprüfung.

Einzelne Bauteilgruppen auf der Leiterkarte waren so schlecht an Masse angebunden, dass eine Fehlfunktion nicht auszuschließen ist.

Die dünnen roten Freihandlinien zeigen den möglichen Stromverlauf von der Einspeisung an einem Schaltreglermodul, zum 3,3V-Schaltregler für die Elektronikversorgung, hin zu den Verbrauchern. Deutlich kann man dem entnehmen, dass der Strom sehr weite Wege nehmen muss, dazu noch mit sehr dünnen Kupferquerschnitt.

Meine Empfehlung zur schnellen und einfachen Verbesserung:

Mit zwei weiteren Lagen für 3,3V und Masse (GND), würden man dieses Problem beseitigen können.

Designfehler: Isolationsabstand in den Zwischenlagen

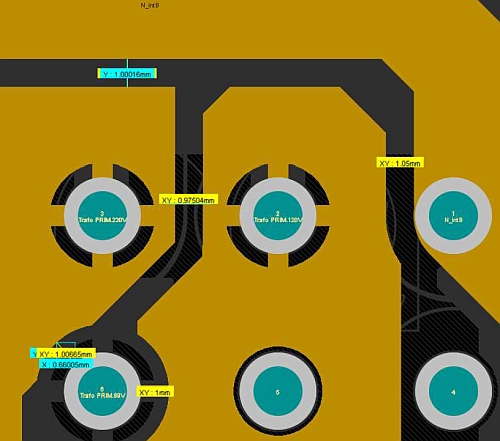

Im zu überprüfenden Elektronikdesign wurde ein Trafo verwendet, der als Spartrafo ausgelegt war, um verschiedene Spannungen aus der 230Vac Netzspannung zu erzeugen.

Die dort vorzufindenden Potenziale lagen bei 230Vac, 120Vac und 89Vac. Im Extremfall konnte die Spannungsdifferenz 185Vpk zwischen den Bauteilanschlüssen betragen.

Auch wenn das mit Harz versehene Glasgewebe des Leiterplatten-Basismaterials ein Isolator darstellt, mit einer deutlich höheren Spannungsdurchschlagsfestigkeit als Luft, scheint hier ein Abstand von 1mm zu gering zu sein.

Hier ist das Problem hausgemacht, da es keinen Grund dafür gibt, die Abstände derart zu verringern.

Auf dem obigem Bild kann man gut kennen: oberhalb vom Pin 2 und Pin 3 wird kein Strom fließen, weil dies für den Strom keinen Sinn macht. Durch die nach oben verlängerter Fläche, verringert dies aber unnötig den Abstand zum Nachbar-Potenzial.

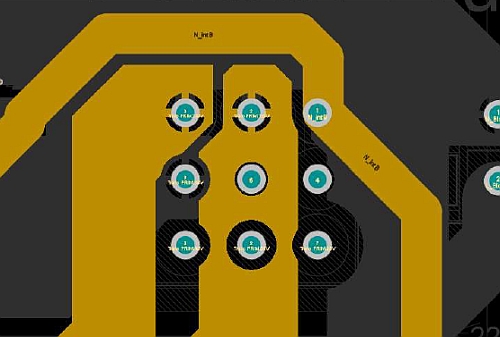

Auf den nachfolgenden Bildern haben wir einen Vergleich des Original Layouts mit einer von uns optimierten Version dargestellt.

Kein Pin in der optimierten Version erhält weniger Fläche für den Strom, aber mit deutlich mehr Abstand zu den Nachbar-Potenzialen.

Selbst unser Vorschlag ließe sich noch besser optimieren. Wir wollten hier auch nur optisch den Unterschied darstellen.

Die Verwendung von Wärmefallen an den Pads sind bei einer Anpassung der Bahnbreiten am Pad auch nicht mehr notwendig.

Zudem wird fertigungstechnisch sehr wahrscheinlich ein Wellenlötprozess zum Einsatz kommen, der die komplette Baugruppe entsprechend für das Löten vorheizt.

Designfehler: Verlegung des Masse-Potenzials (Ground / GND) und des isolierten Masse-Potenzials (ISO-GND)

Im folgenden Projekt beklagte sich der Kunde, dass seine Schaltung auf dem Labortisch sein Funktion erfüllt, aber nicht im Feld beim Kunden. Es würde sich ständig die Schaltung aufhängen und hätte bis zum nächsten Power OFF / Power ON keine weitere Funktion mehr.

Für einen Test zur Reproduktion des Fehlers im Labor, empfahl ich ihm, ein Piezo-Feuerzeug in relativer Nähe zur Schaltung zu zünden.

Siehe da, dieser kleine EMV-Test zeigte seine Wirkung und die Schaltung fiel auch schon im Kunden-Labor aus.

Die Schaltung beinhaltet einen Mikrocontroller sowie einen isolierten Bereich für das digitale I/O.

Von der Idee her schon gut gelöst, war der Einsatz eines isolierten Bereiches, um die Aussenwelt von der Innenwelt der Schaltung zu trennen. Ein DCDC-Wandler erzeugt die isolierte Spannung für die Sekundärseite (Aussenwelt) der Optokoppler.

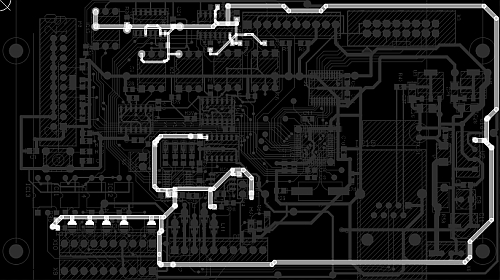

Zuerst wurde die Verlegung der Masse und der 3,3V-Versorgung geprüft.

Wenn man sagen würde, die Verlegung war Suboptimal ausgeführt, wäre das reines Schönreden.

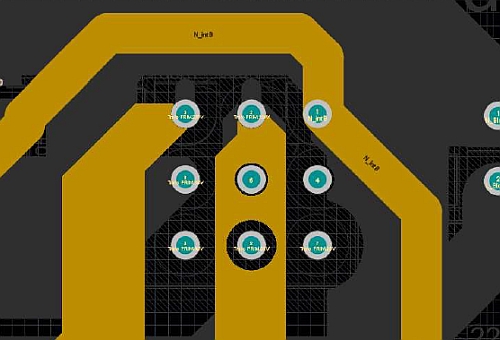

In obigem Bild ist die Masse-Verdrahtung (GND) gehighlighted. Die Führung der Masse wurde nicht Sternförmig ausgelegt. Diese "nach-ein-ander" verdrahtete Masse hat zur Auswirkung, dass einzelne Bauteile mit schnellen Schaltflanken Spannungsstörungen induzieren, die wiederum andere Bauteile dann stören.

Ein anderes, durchaus größeres Problem aber war, dass zwar ein isolierter Bereich für das I/O zur Aussenwelt vorgesehen war (zumindestens im Schaltplan), aber nicht nach den Regeln mit Isolationsabstand zu internen Leiterbahnen und Bauteilen umgesetzt wurde. Die beiden Leitungen für GND-Iso und 3,3V-Iso verliefen wild über die Platine verteilt und gaben allen und jedem die Chance, Störungen von Aussen nach Innen zu koppeln.

Im obigen Bild kann man das GND-Iso-Potenzial gehighlighted erkennen. Auch kann man erkennen, dass dies auch unter und neben Bauteilen udn Verdrahtung interner Potenziale liegt.

Es gab irgendwie kein Konzept für die normale Spannungsversorgung, als auch natürlich nicht für die isolierten Bereiche.

Gelöst haben die Problemstellen dadurch, dass wir zum Einen zwei weitere Lagen für Versorgungspotenziale eingefügt haben und zum Anderen einen Bereich auf dem Layout als isolierten Bereich ausgewiesen und dort alle Optokoppler versammelt haben.

weitere Dienstleistungsbereiche:

- Sachverständiger / Gutachter

- Elektronikentwicklung, analoges und digitales Schaltungsdesign

- 3D-Modeling mit Altium Designer

- Änderungen an Platinen / Redesigns

- Nachbau von Platinen / Re-Engineering

- digitales Schaltungsdesign mit VHDL auf ALTERA und XILINX FPGA

- Mikroprozessorentwicklung mit Microchip PICs

Qualitätsmanagement nach

DIN EN ISO 9001:2015

Mitglied im

Fachverband für Elektronik-Design

und -fertigung e.V. (FED)